Modern Systems-of-Systems (SoS) and Systems-on-Chip (SoC), including military systems, consist of heterogeneous and often distributed components that not only interact among themselves, but also with the physical world via wireless networks (such as radio), sensors and actuators. This interaction can be a source of malfunctioning of the system, due to the heterogeneous nature of analog and digital components involving many A/D and D/A interfaces, but also due to the complex timing constraints resulting from the distribution of the components. Systematic verification and validation techniques, used extensively in the digital domain, are still in their infancy for analog and mixed-signal (AMS) systems. The nature of analog systems, the very high cost of their simulation, the complex interactions between analog and digital components as well as the cultural background of AMS designers make the proliferation of verification technology to the AMS domain an extremely difficult and challenging task. Thus verification and validation represent today the most important bottleneck in the design process of AMS systems.

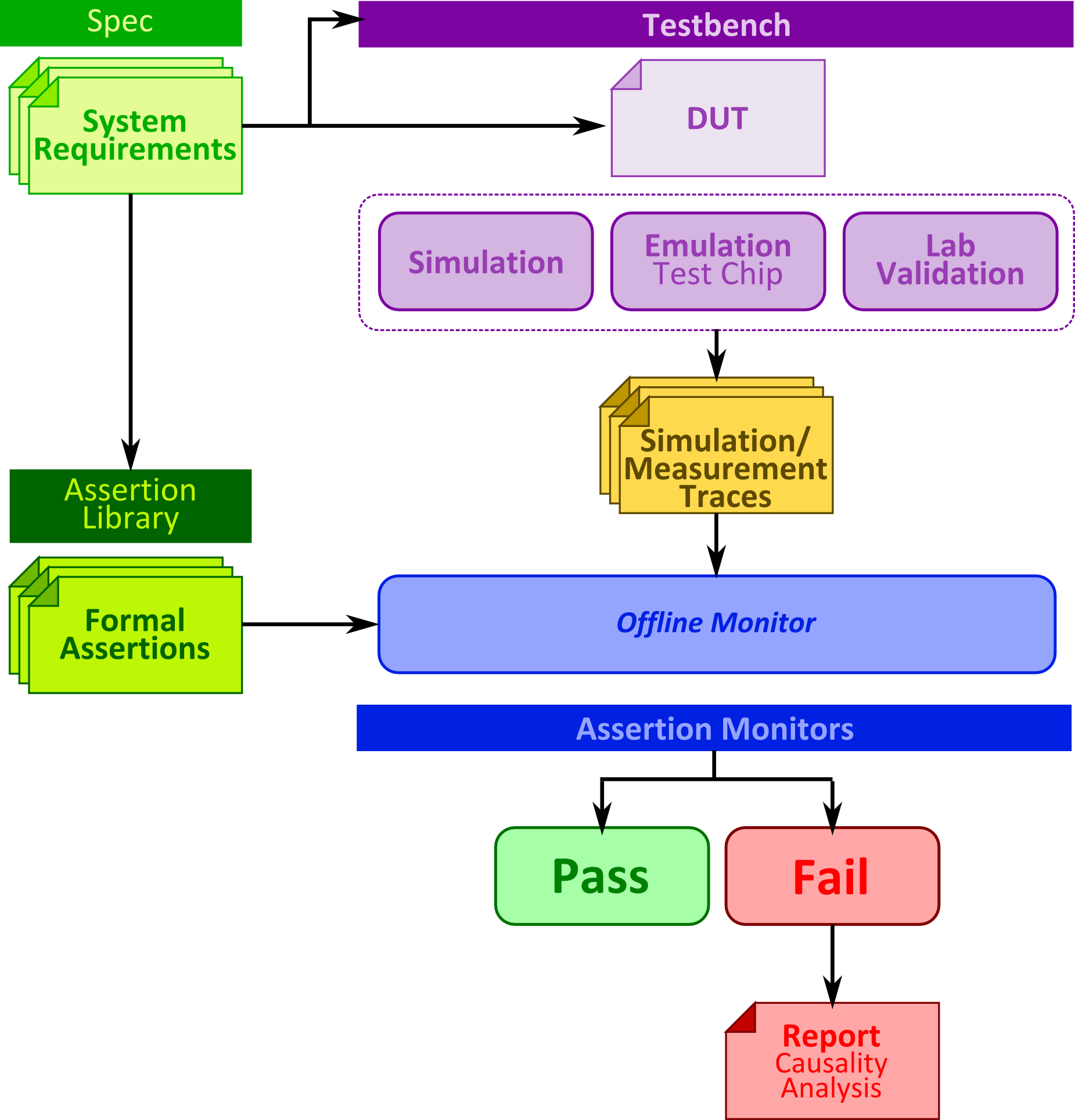

MISTRAL will improve this situation by providing a framework for AMS assertion-based verification. In this framework, correctness requirements of the system will be formally written down using an assertion language capable of expressing interface properties between analog and digital components, as well as the complex timing relationships due to communication delays. We will develop a tool which will read simulation traces and detect violation of assertions, thus automating part of the AMS verification process. MISTRAL will build upon the previous pioneering work of the consortium members on assertion-based AMS verification methodology, centered on the assertion language STL (Signal Temporal Logic) and the monitoring tool AMT, so as to enhance this technology and bring it from a proof-of-concept to a new stage, which will incorporate mature theoretical developments done in MISTRAL. The enhancements developed in the project will be driven by a real-life case study, the chip-set for the control of power transistors, which will also serve as the final test-bench for the applicability of the new methods and tools.

The outcome of MISTRAL will improve the competitiveness of the European embedded systems civilian and military industry, by significantly reducing verification time in the AMS systems design process.

Facts:

- Project start: 09/12/2014

- Project duration: 2 years

- Funding: European Defence Agency (EDA) JIP ICET 2

- Coordinator: Dejan Ničković, AIT Austrian Institute of Technology

- Consortium: AIT Austrian Institute of Technology (Austria), VERIMAG, Université Joseph Fourrier (France), EASii-IC (France)

- Contact: dejan.nickovic@ait.ac.at